|

무어의 법칙, 살았나 죽었나? 아니면 부활했나? | |||

| 집적 회로내 트랜지스터 밀도가 더 높아짐으로서 전자 제품의 비용 대비 성... |

|

|  |

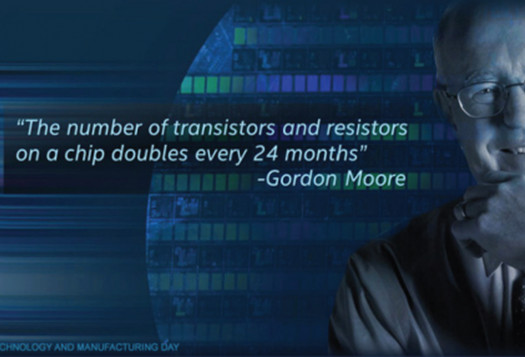

집적 회로내 트랜지스터 밀도가 더 높아짐으로서 전자 제품의 비용 대비 성능은 지속적으로 향상되어 왔다. 인텔의 고든 무어는 이를 정리하여 무어의 법칙을 언급했다. 평방 밀리미터 당 트랜지스터의 수가 약 2년마다 두 배로 증가한다는 것! 그러나 현재에도 이 법칙은 유효한가?

기술경제 혁명을 뒷받침하는 필수적인 토대에는 무어의 법칙이 있다. 알다시피, 무어의 법칙은 집적 회로내 트랜지스터 밀도가 더 높아짐으로서 전자 제품의 비용 대비 성능이 지속적으로 향상되는 것을 의미한다.

이 놀라운 경제 현상은 적어도 60년 동안 진행되어 왔다. 무어의 법칙은 인텔의 고든 무어(Gordon Moore)가 “평방 밀리미터 당 트랜지스터의 수가 약 2년마다 두 배로 증가했었다”고 밝힌 1965년에 처음으로 세상에 널리 알려졌다, 지난 50년 동안 무어의 법칙대로 컴퓨팅과 네트워킹의 비용은 더 낮아졌고, 성능은 더 높고 안정적으로 변모해왔다.

그런데 2018년에 일부 전문가들은 무어의 법칙이 죽었다고 주장한다. 또 다른 사람들은 그렇지 않고 그것은 여전히 살아 있다고 말하고 있다. 그리고 또 다른 사람들은 그것이 새로운 형태로 부활했다고 주장한다. 누가 옳은 것일까? 사실 중심으로 살펴보자.

우리는 5년 전 2013년에 무어의 법칙에 대해 언급했다. 그리고 5년이 흐른 2018년을 기준으로 이야기해보자. 5년 전의 무어의 법칙과 이후 2018년의 상황에는 어떠한 차이점이 있을까? 5년 동안, 우리는 실제적으로 일어난 일을 되돌아보고 가능성있는 앞으로의 궤도를 이해해야 할 것이다.

디지털 컴퓨팅이 옥수수에 물을 주고 경작하는 것부터 뇌 깊숙한 곳에서 암 초기 진단을 내리는 것에 이르기까지 사람이 하는 거의 모든 일을 주도하는 시대에, 경제의 미래라는 사안보다 더 중요한 것은 없을 것이다. 오늘날 끊임없이 증가하는 컴퓨팅 성능과 그에 대한 비용 절감은 모든 것들이 모든 곳에 연결되는 기계 지성을 구현되게 만들었다. 그래서 이 현상의 갑작스러운 결말은 인간 진보의 궤적을 돌이킬 수 없을 수준으로 변화시킬 것이라는 데 있다.

다행히 인텔의 리더들이 옳다면, 그 변화는 어느 순간 곧바로 일어나지 않을 것이다. 그들은 이렇게 말한다.

“우리는 다음 5년 동안 [무어의 법칙으로] 문제를 어떻게 해결할 것인가에 대해 상당한 통찰력을 갖고 있습니다.”

그들은 또한 5년 동안 수많은 경로 찾기를 하고 있다. 오늘날 결론은 이렇다.

“인텔에 있어 무어의 법칙은 여전히 잘 살아있습니다.”

그렇다면 무어의 법칙이 완전히 죽지는 않았지만 과거와 달리 생생하진 않다고 주장하면서 많은 다른 전문가들은 왜 이러한 인텔의 주장에 도전하는 것일까? 답은 정의에 있다.

“1평방 밀리미터 당 트랜지스터의 수가 대략 2년마다 2배로 증가된다”는 1965년 무어의 관찰을 문자 그대로 해석해보자. 1밀리미터의 실리콘 위에 더 많은 트랜지스터를 패킹할 수 있는 역량의 대부분은 각 칩의 크기를 더 작게 만드는 것을 포함한다. 예를 들어, 65나노미터(nm)에서 45나노미터로 이동한다는 것은 엔지니어들로 하여금 1밀리미터 실리콘 위에 대략 2배 더 많은 트랜지스터를 패킹할 수 있게 해준다. 고든 무어는 1밀리미터의 실리콘 비용이 일정하게 유지된다고 가정했는데, 이것은 2년마다 한 세대에서 다음 세대로 이동하면서 트랜지스터 당 비용이 거의 절반 정도가 된다는 것을 의미한다.

그러나 최근 수년 동안 이러한 가정에 있어 두 가지 일이 벌어졌다.

1. 기술 세대간 시간 간격이 더 길어졌다.

2. 완성된 1밀리미터 실리콘을 생산하는 비용이 늘어났다. 가장 최신 기술을 개발하고 배치하는데 드는 비용이 너무 크기 때문이다.

어떤 사람들은 무어의 법칙이 죽었다고 말한다. 이제는 더 이상 2년마다 그 크기를 절반으로 줄이는 것이 불가능하기 때문이다. 그 외 다른 모든 것들이 동등하다면, ‘비용과 기능’ 개선의 정도가 더 이상 2년마다 두 배가 되지 않는다는 것을 의미한다.

그러나 이야기는 여기에서 끝나지 않는다. 현재 그리고 부상하고 있는 10나노미터와 7나노미터 기술에 있어 그 밀도가 더 빠르게 증가하고 있다. 이는 칩의 크기가 작아지고 있다는 것을 의미한다. 따라서 22나노미터와 14나노미터, 14나노미터와 10나노미터 사이의 세대 이동의 시간 간격이 길어지더라도, 인텔은 매년 똑같이 개선을 이루고 있는 것이다. 실제로 인텔은 14나노미터로 이동하면서, 그리고 10나노미터로 이동하면서 더 큰 밀도의 혜택을 가져가고 있다. 본질적으로 이들은 세대 이동을 통해 더 큰 진보를 이루고 있으며, 역사적인 비용 대비 성능 향상 트렌드를 계속 유지하고 있다.

인텔은 하이퍼스케일링(hyperscaling)이라는 전략으로 이를 실행해올 수 있었다. 이것을 가능하게 하는 몇 가지 기본 기술이 있지만, 실제로 중요한 것은 자기 정합형 더블 패터닝(SADP, Self-Aligned Double Patterning) 기술과 자기 정합형 쿼드 패터닝(SAQP, Self-Aligned Quad Patterning) 기술이다.

SADP는 다른 말로 측벽 기술이라고도 한다. 재료의 양쪽 측벽 패턴을 생성해 2개가 모여 있는 라인을 형성하기 때문이다. SAQP는 이러한 SADP를 두 번 반복하는 것이다.

이 새로운 기술은 밀리미터당 비용은 높이지만 밀리미터당 더 많은 트랜지스터 패킹을 가능하게 한다. 결과적으로 웨이퍼를 제조하는 데 필요한 제곱 밀리미터당 비용은 상승하지만 인텔은 트랜지스터를 수축시킨다. 이로 인해 인텔은 매번 트랜지스터 당 비용을 감소시킨다. 결과적으로 트랜지스터 당 비용이 천천히 더 향상된 속도로 내려가고 있다. 그래서 인텔은 “무어의 법칙은 살아 있고 잘 있다”고 이야기하는 것이다.

소비자와 애플리케이션 개발자에게 있어, 여전히 지속되는 ‘무어의 법칙’의 혜택은 반도체 산업이 성능을 향상시키고, 기능을 추가하고, 비용을 절감하는 것을 동시에 이룰 수 있다는 의미가 된다.

이러한 사실과 전망을 볼 때, 우리는 다음과 같은 5가지를 예측할 수 있다.

첫째, 향후 10년 동안 CMOS 집적 회로에 대한 비즈니스가 일반화될 것이다.

개별 크기를 더 작게 만드는 것 외에도 다중 레이어 칩을 제작하는 것도 가능하다. 그러나 두 경우 모두의 문제는 방열(heat dissipation)이다. 향후 5년은 주로 우수한 실행 혹은 성능의 문제일 것이고, 그 이후부터는 새로운 장벽을 넘어서기 위한 산업 혹은 기업의 창의력 문제가 될 것이다.

둘째, 중단기적으로 황의 법칙(Huang’s Law)으로 불리는 또 다른 패러다임이 그래픽 처리 장치(GPU, graphic processing unit)의 힘을 사용할 수 있는 수많은 상업적 적용에 있어 더 중요해질 수도 있다.

엔비디아(Nvidia)의 CEO 젠슨 황(Jen Hsun Huang)은 최근, ‘오늘날 엔비디아의 GPU가 5년 전보다 25배 더 빨라졌다’고 밝혔다. 이것은 아주 큰일이다. 그들이 무어의 법칙에 따라 진보하고 있었다면 그 속도는 약 10배 증가했을 것이다. 더욱 인상적인 점은 신경 네트워크 알렉스넷(AlexNet)을 1500만 개의 사진을 통해 훈련시키는데 필요한 시간이 불과 6일이었다는 점이다. 그것도 5년 전의 이야기다. 그렇다면 지금은? 18분이면 충분하다. 무려 500배나 더 빨라진 것이다! 어떻게 이런 일이 가능했을까? 이러한 어플리케이션의 기계들은 다양한 분야의 선두들이 진보할 때 그들로부터 동시에 혜택을 수령받기 때문이다. 건축, 인터커넥트, 메모리 기술, 알고리즘 등과 같은 분야가 그것이다. 이러한 혁신은 전 분야를 아우른다.

셋째, 소위 ‘뉴로모픽(Neuromorphic, 뇌 신경 모방)’ 칩이 인공지능의 상업화에 중요한 역할을 할 것이다.

2020년대의 가장 큰 상업적 기회는 인공지능에 의해 주도될 가능성이 있으며, 뉴로모픽 칩이 큰 역할을 할 것이다. 인텔의 과학자 찰스 어거스틴(Charles Augustine)의 연구 보고서는 뉴로모픽 칩은 인지 컴퓨팅, 적응형 인공 지능, 감지 데이터, 연상기억장치(associate memory)와 같은 인공지능 작업을 처리할 수 있을 것이라고 예측한다. 이 칩은 또한 최고의 CMOS 칩이 사용하는 것보다 15∼300배나 더 적은 에너지를 사용한다.

이것은 아주 의미심장한데, 시리(Siri)와 알렉사(Alexa)와 같은 오늘날의 인공지능 서비스들이 음성 질문이나 명령에 응답하는 것과 같은 작업을 수행하기 위해 클라우드 기반 컴퓨팅에 의존하기 때문이다. 스마트폰은 인공지능에 필요한 알고리즘을 사용하는 컴퓨팅 성능을 보유하지 않은 칩으로 가동한다. 따라서 스마트폰에 그러한 성능이 있는 칩이 사용될 경우, 배터리는 바로 방전되어 것이다. 따라서 초저전력 뉴로모픽 칩은 향후 스마트폰에도 적용될 수 있을 것이다. 당연히 스마트폰의 성능은 지금과 비교가 되지 않을 것이다.

넷째, 광학 테라헤르츠(teraherts) 칩이 초고속 광통신 컴퓨팅 기술과 CMOS를 통합할 수 있도록 해줄 것이다.

최근 「레이저 앤 포토닉스 리뷰(Laser and Photonics Review)」에 게재된 바와 같이, 히브리 대학교(Hebrew University)의 나노 옵토 그룹(Nano-Opto Group)은 광통신의 속도와 기존 전자 제품의 안정성, 제조 확장성을 통합하는 광학 기술을 개발했다. 광통신은 초고속이지만, 마이크로 칩 조건에 안정성이 떨어지고, 대량으로 복제하기도 힘들다. 이제 금속-산화-질화물-산화 실리콘(Metal-Oxide-Nitride-Oxide-Silicon, 또는 MONOS) 구조를 사용하여 히브리 대학 팀은 마이크로 칩에 플래시 메모리 기술을 활용하는 새로운 집적 회로를 개발했다. 개발이 완료되기만 하면, 이 기술은 표준 8∼16 기가헤르츠 컴퓨터를 100배 더 빠르게 작동시키고, 상용 테라헤르츠 칩의 시대에 더 근접시키게 될 것이다.

다섯째, 무어의 법칙이 2025∼2035년 사이에 심각한 병목 현상을 겪게 될 때까지 그래핀(Graphene) 기반의 로직이 상업용 전자제품에 있어 큰 역할을 하기 시작할 것이다.

2013년부터 연구자들은 그래핀 나노시트(nanosheets, 10억분의 1시트)를 전자 기술로 전환시키는데 큰 진전을 이루었다. 2030년까지 수백의 기가헤르츠로 작동하는 비용 효율적인 그래핀 마이크로프로세서를 제작하는 것이 가능할 것이다. 그때, CMOS는 그래핀에게 자리를 넘겨주기 시작할 것이고, 무어의 법칙은 마침내 끝나게 될 것이다. 그리고 우리는 새롭고 역시나 흥미로운 성능 곡선으로 진일보하게 될 것이다.

* *

References List :

1. Meir Grajower, Noa Mazurski, Joseph Shappir, Uriel Levy. Laser & Photonics Reviews, 2018; 1700190. Non-Volatile Silicon Photonics Using Nanoscale Flash Memory Technology.

https://onlinelibrary.wiley.com/doi/abs/10.1002/lpor.201700190

2. Steven Vannelli, CFA. Knowledge Leaders Capital Blog, April 7, 2017. Moore’s Law: Knowl- edge Economy Firmly On Track.

http://go.gavekalcapital.com/l/109202/2017-04-05/4d6d-nd/109202/37625/Moore_s_Law_and_the_Knowledge_Effect.pdf

3. Dave James. Pcgamesn.com, January 1, 2018. Intel, Nvidia, Please Shut Up About Moore’s Law. It’s Not Dead Yet, or Interesting... or Even a Law.

https://www.pcgamesn.com/intel-moores-law-no-more

4. Tom Simonite. MIT Technology Review, May 30, 2017. How AI Can Keep Accelerating After Moore’s Law.

https://www.technologyreview.com/s/607917/how-ai-can-keep-accelerating-after-moores-law/

|  |

|

Moore’s Law: Alive? Dead? Or resurrected?

The indispensable foundation underpinning the Fifth Techno-Economic Revolution is Moore’s Law, the relentless cost-performance improvement in electronics enabled by the ever-increasing density of transistors in integrated circuits.

This amazing economic phenomenon has been going on for at least 60 years. It was first widely-recognized back in 1965, when Intel’s Gordon Moore observed that “the number of transistors per square millimeter was doubling approximately every two years.” For over 5 decades that has translated into lower costs, higher performance and more reliable computing and networking.

In 2018, some experts argue that Moore’s law is dead. Other say it’s alive and well. And others claim it has been resurrected in a new form. Who’s right?

Consider the facts.

We last examined Moore’s Law, in 2013, as we were writing Ride the Wave. Now, five years later, we’re looking back at what actually transpired and attempting to understand its likely forward trajectory.

In an era when digital computing drives nearly everything we do, from plowing and watering fields of corn to diagnosing early-stage cancer deep inside the brain, no issue is more important for our economic future. Today, the ever-falling cost of ever-increasing computing power lets us embed connected “machine intelligence” into nearly everything, everywhere. So, the sudden end of this phenomenon would irrevocably change the trajectory of human progress.

Fortunately, if the leaders at Intel are right, that won’t happen anytime soon. They say, “We have good insight into how we will solve the problems [with Moore’s Law] during the next five years.” They also do a lot of path-finding for the five years beyond that point. The bottom line: as of today, “Moore’s Law is alive and well, for Intel.”

So, why do a lots of other experts challenge Intel’s claim, insisting that Moore’s Law is sick, if not totally dead. The answer lies in definitions.

Consider the literal wording of Moore’s 1965 observation, “the number of transistors per square millimeter doubles approximately every two years.” Much of the ability to pack more transistors onto a millimeter of silicon involves making individual feature on the chip smaller; for instance, going from 65 nm features to 45 nm features permitted engineers to pack roughly twice as many transistors onto a single millimeter of silicon. Gordon Moore assumed that the cost of a millimeter of silicon would remain constant in real dollars meaning that the cost per transistor would be half as much as you move from one generation to the next about every two years.

But two things have happened to those assumptions in recent years:

1. The time intervals between generations of technology have become longer; and

2. The cost of producing a finished millimeter of silicon has increased because the newest technology is so expensive to develop and deploy.

Some people say Moore’s law is dead because it’s no longer possible to cut the size of features in half every two years. All other things being equal, that implies that the amount of improvement in cost and functionality would no longer be doubling every two years.

However, there’s more to the story. For current and emerging 10-nanometer and 7-nanometer technology, the density is actually increasing faster that implied by the shrinking size of chip features. So, Intel is getting the same year-on-year improvement, even as the time intervals between 22-nanometer and 14-nanometer as well as between 14-nanometer and 10-nanometer, have become longer. In fact, Intel is a larger-than-normal density benefit as they went from 14-nanometer and as they go to 10-nanometer. In essence, they’re taking bigger steps from generation-to-generation, which is enabling them to stay on the historical cost-performance trend line.

Intel has been able to do that because of a strategy called hyperscaling. There are several underlying technologies that enable this, but the really important ones are called Self-Aligned Double Patterning, and Self-Aligned Quad Patterning.

This new technology raises the cost per millimeter but also permits more transistors per millimeter. As a result, in every generation cost per square millimeter to manufacture wafers goes up, but Intel shrinks the transistors. And at the end of the day, they get a declining cost per transistor. As a result, their cost per transistor is coming down at a slightly better rate than the historical trend. That is why they say, “Moore’s Law is alive and well.”

For consumers and application developers the benefit of continuing Moore’s Law is that the semiconductor industry can improve performance, add features, and reduce costs, all at the same time.

Given this trend, we offer the following forecasts for your consideration.

First, it will be business-as-usual for CMOS integrated circuits over the coming decade.

In addition to making individual features smaller, it’s also possible to produce multi-layer chips. But the problem in both cases is heat dissipation. The next five years is largely a matter of good execution. Beyond that point, we’ll have we’ll have to rely on the ingenuity of the industry to overcome significant barriers.

Second, in the medium term, another paradigm called Huang’s law may become more important for many commercial applications that can harness the power of GPUs.

CEO Jen-Hsun Huang recently pointed out that today, Nvidia’s GPUs are 25 times faster than they were just five years ago. That’s big; if they were advancing according to Moore’s law, they would only have increased their speed by a factor of ten. Even more impressive, the time required to train AlexNet, a neural network trained on 15 million images took six days, five years ago; now it takes just 18 minutes. That’s 500 times faster! Why? Because, these machines in these applications benefit from simultaneous advances on multiple fronts: architecture, interconnects, memory technology, algorithms, and more. The innovation is across the entire stack.

Third, so-called neuromorphic chips will paly an important role in commercializing artificial intelligence.

The biggest commercial opportunities of the 2020s are likely to be driven by AI, and Neuromorphic chips will play a big role there. A research paper by Intel scientist Charles Augustine predicts that neuromorphic chips will be able to handle artificial intelligence tasks such as cognitive computing, adaptive artificial intelligence, sensing data, and associate memory. They will also use 15-to-300 times less energy than the best CMOS chips use. That’s significant because today’s AI services, such as Siri and Alexa, depend on cloud-based computing in order to perform such feats as responding to a spoken question or command. Smartphones run on chips that simply don’t have the computing power to use the algorithms needed for AI, and even if they did, they would instantly drain the phone’s battery.

Fourth optical terahertz chips will enable CMOS to integrate with super-fast photonic computing technology.

As documented recently in Laser and Photonics Review, Hebrew University’s Nano-Opto Group has created an optic technology that integrates the speed of optic communications with the reliability and manufacturing scalability of conventional electronics. Optic communications are super-fast but in microchips they become unreliable and difficult to replicate in large quantities. Now, by using a Metal-Oxide-Nitride-Oxide-Silicon (or MONOS) structure, the Hebrew University team has come up with a new integrated circuit that uses flash memory technology in microchips. Once fully developed, this technology could enable standard 8-to-16 gigahertz computers to run 100 times faster and bring us closer to a commercial terahertz chip. And,

Fifth, by the time Moore’s Law hits a serious bottleneck between 2025 and 2035, Graphene-based logic will begin to play a huge role in commercial electronics.

Since 2013, researchers have made a great deal of progress in terms of transforming graphene nanosheets into an electronic technology. By 2030, it will be possible to manufacture cost-effective graphene microprocessors operating at hundreds of gigahertz. At that point, CMOS will begin to yield share to graphene. Moore’s law will finally be finished. And, we’ll have jumped onto a new and equally exciting performance curve.

References

1. Meir Grajower, Noa Mazurski, Joseph Shappir, Uriel Levy. Laser & Photonics Reviews, 2018; 1700190. Non-Volatile Silicon Photonics Using Nanoscale Flash Memory Technology.

https://onlinelibrary.wiley.com/doi/abs/10.1002/lpor.201700190

2. Steven Vannelli, CFA. Knowledge Leaders Capital Blog, April 7, 2017. Moore’s Law: Knowl- edge Economy Firmly On Track.

3. Dave James. Pcgamesn.com, January 1, 2018. Intel, Nvidia, Please Shut Up About Moore’s Law. It’s Not Dead Yet, or Interesting... or Even a Law.

https://www.pcgamesn.com/intel-moores-law-no-more

4. Tom Simonite. MIT Technology Review, May 30, 2017. How AI Can Keep Accelerating After Moore’s Law.

https://www.technologyreview.com/s/607917/how-ai-can-keep-accelerating-after-moores-law/

_아침독서상단(2).jpg)

.jpg)

.jpg)

.jpg)